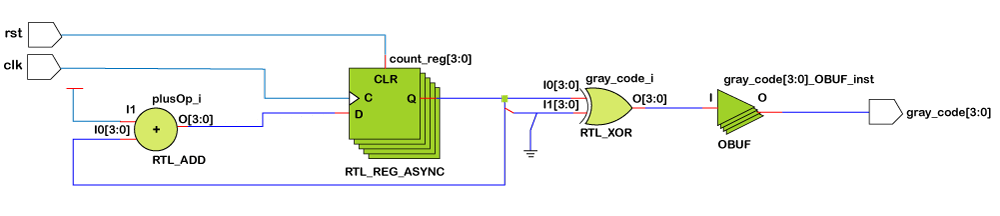

Parameter integer setval = 0 from outval = (outval +(+up- !up)*stepsize)%(1<<`SIZE) So whenever the enable is greater than threshold, the count up/down should go on otherwise output of the counter should be zero.Īs I dont know verilogA, i have tried to understand your code and modified it to include the enable input. I would like to add enable input signal to the counter. Thank you very much for sharing the code. Parameter integer up = 0 from //0=increasing 1=decreasingĪnalog outval = (outval +(+up- !up)*stepsize)%(1<<`SIZE) Parameter real ttol = 0 // time tolerance on the clk It prevents glitches from appearing during the counting process, and. Parameter real vtol = 0 // signal tolerance on the clk A Gray code is a reordering of bits in a counter so that only one bit changes at a time. Do you see what I'm doing wrong in the code? Thanks!!! So, I got only the first increment=2 making all the following outputs wrong. I defined parameter stepsize that is the desired increment.īelow the code: it has 4 bits and stepsize=3.

#2 BIT GRAY CODE COUNTER VERILOG CODE HOW TO#

So you don't reset you module, you don't send a load at a rising edge, and you are complaining your output is at X? Well, you should re-read all the basics of Verilog, and learn how to properly use a simulator.I'm modeling a binary counter in VerilogA. Lastly, have you checked in you waveform that you have a rising edge at the same time you send a load signal level high? As far as I have read your test bench I do not believe this occurs. To monitor whether the number of clock cycles is even or odd, a dummy bit Dum is added and used for this purpose. Note that B0 toggles every two clock cycles. Gray code counters (and other related counters) count through all 2n binary numbers, but not in a natural counting sequence (only 1 bit changes between. Using this observa-tion, asystematicwaytocomeupwith a N-bit gray code. Any number could be adjacent to N other numbers in a gray code sequence. This is surely a malpractice, the first thing you should do, before pumping any data into your module is to reset it. Fig.2 Gray code counter memory: Circuitry The operating principle of the Gray counter/memory can be explained by examining the case of the 3-bit Gray code sequence, given in Table I. For example a sequence for a 2-bit gray code counter is 00 01 11 10 Come up with a 3-bit gray code sequence and write a Verilog module, Gra圜odeCounter, which is a gray code counter with this sequence. I have also noticed you do not perform a reset in your module. As the synthesizer won't be capable of doing that, you are going to have hardware behavior which is not modeled by you simulation.

#2 BIT GRAY CODE COUNTER VERILOG CODE SIMULATOR#

I don't know what the simulator will do, but probably he will change q signal as soon as it executes this line, and not at the next rising edge clock as you should expect. It does not make any sense, you are modeling a sequential output, you should model it using a non-blocking assignment like: "q <= q << 1" and "q <= temp". What is not OK, is continuing using blocking assignments in "q = q << 1" and in "q = tmp". Secondly, in you else statement, you are using a blocking assignment in "tmp = q" which is ok, because it stores q value in a variable internal to the process. And I am not sure if I follow why you are using it, given you have already a reset state for it. My guess is that the state never goes off from s0.Īny tips on how I should implement the codes?įirst of all, initial commands are not used in synthesizable Verilog code. When I run a test cases on it, it somehow only prints s0 and seems to be constant throughout the execution. When control variable is 0, I want to execute s0,s1,s2,s3,s4,s5, and so on as you can see(BCD), and when control variable is 1, I want to execute s0,s1,s3,s2,s6,s7,s5,s4 respectively (gray code) 2nd state: 001, 3rd state: 010 and so on Reg state // there will be 8 states: 1st state :000 Here is my implementation: module grayBCDcounter( If the input control = 0, the circuit will count in BCD and if the input control = 1, the circuit will count in gray code sequence. I am trying to implement a 8-bit counter that does both BCD(Binary Code decimal) and gray code sequence.

0 kommentar(er)

0 kommentar(er)